很多装机新手一看到锐龙内存相关讨论,就会被一堆词直接劝退:FCLK、UCLK、MCLK、分频、不分频、1:1、1:2、2:3:3……

看着像很复杂,其实核心问题只有一个:内存跑得快,不代表整条传输链路都跟得上。如果 CPU 里面有一段速度没跟上,那纸面频率再漂亮,实际效果也可能打折。

所以这篇不讲太硬的理论,也不堆太多参数。我就用装机用户更容易懂的方式,把锐龙内存模式这件事讲明白。你看完之后,至少会知道:

- 为什么大家老说锐龙要看 1:1

- 为什么频率更高不一定更好

- 为什么有些平台 6000 很香,有些继续往上冲却不一定值

先把最常见的 3 个词看懂

MCLK:内存本身的速度

这个最好理解。比如 DDR4 3200、DDR5 6000,这些就是我们平时最常说的“内存频率”。

如果换成更底层一点的说法,大致可以简单理解成:

- DDR4 3200,对应 MCLK 约 1600

- DDR5 6000,对应 MCLK 约 3000

记不住也没关系,你只要知道:MCLK 说的是内存自己跑多快。

UCLK:内存控制器的速度

内存控制器可以理解成 CPU 里负责和内存对接的那部分。

如果内存本身很快,但控制器速度掉队,那就像路修宽了,收费站却没扩建,最后还是会堵。

所以 UCLK 能不能跟上,直接关系到内存效率会不会被打折。

FCLK:锐龙内部的数据通道速度

这个就是大家最容易听懵的那个词。

你可以直接把 FCLK 理解成:锐龙 CPU 内部一条很关键的运输通道速度。

很多代锐龙处理器里,CPU 核心访问内存控制器,中间都要靠这条通道传数据。所以只要 FCLK 跟不上,整个表现就可能受影响。

为什么很多人说“1:1 最舒服”

因为在很多锐龙平台上,MCLK 和 UCLK 保持 1:1,通常意味着整体效率比较好。

再往前一些代数,大家还会一起看 FCLK,追求一种更协调的状态。你可以把它理解成三个人一起搬东西:

- 一个人跑得快

- 一个人跑得慢

- 中间还要互相等

那整体效率就不可能最好。

所以大家常说的“1:1 很香”,本质上不是迷信某个数字,而是在说:各段速度配合得比较顺。

分频到底是什么意思

所谓分频,说白了就是:某一段跟不上了,只能换一种比例去跑。

最常见的情况是:内存频率继续往上提了,但内存控制器或者 FCLK 跟不上,只能让它们按更低的比例运行。

这样做的好处是可以把内存频率继续拉高;但坏处也很明显——传输链路不再整齐,效率会打折。

这也是为什么有些人会发现:

- 内存频率明明更高了

- 跑分却没想象中涨那么多

- 甚至有些场景体感变化很小

原因不是内存没提升,而是别的地方成了短板。

早期锐龙:先别谈极限,能稳就已经不错

在 Zen1、Zen+ 那个阶段,锐龙平台给很多人的印象就是:内存真的挺挑。

那时候很常见的情况是:

- 标称 3200 的条子,不一定真能稳 3200

- 3000、2933 反而更容易稳定

- 再往上就可能蓝屏、报错、进不了系统

所以早期锐龙玩家关注的重点,往往不是“怎么冲到最高频”,而是“怎么在一个合理频率上稳定使用”。

如果你玩过那几代平台,应该对这种体验不会陌生。

Zen2 / Zen3:为什么 DDR4 3600 经常被说成甜点位

到了 Zen2 / Zen3,情况开始变了。

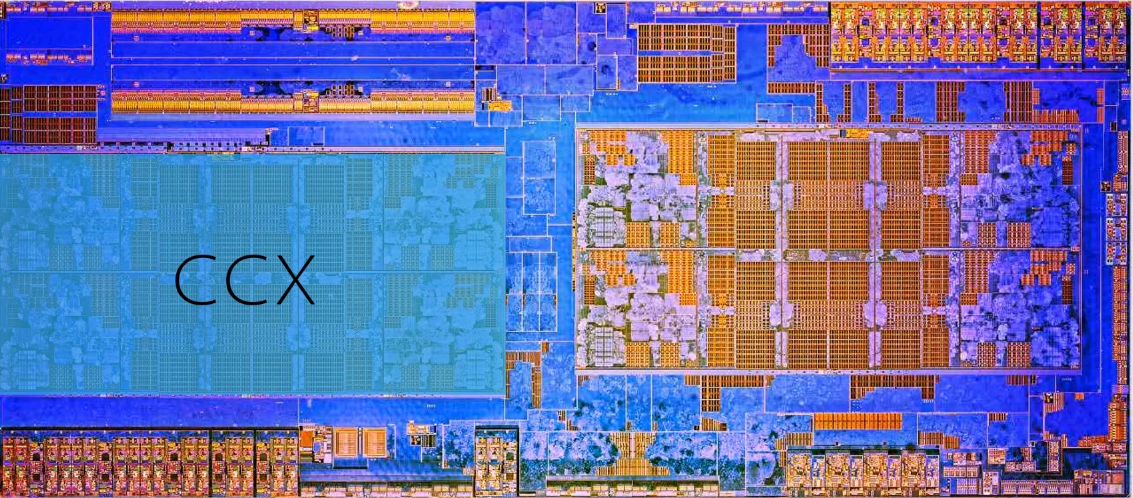

AMD 用了更典型的 Chiplet 设计后,CPU 核心和 I/O 部分的关系变得更依赖内部通道。这个时候,FCLK 的存在感一下就上来了。

问题也跟着出现:

- 内存频率还能继续升

- 但 FCLK 不一定能一直同步升

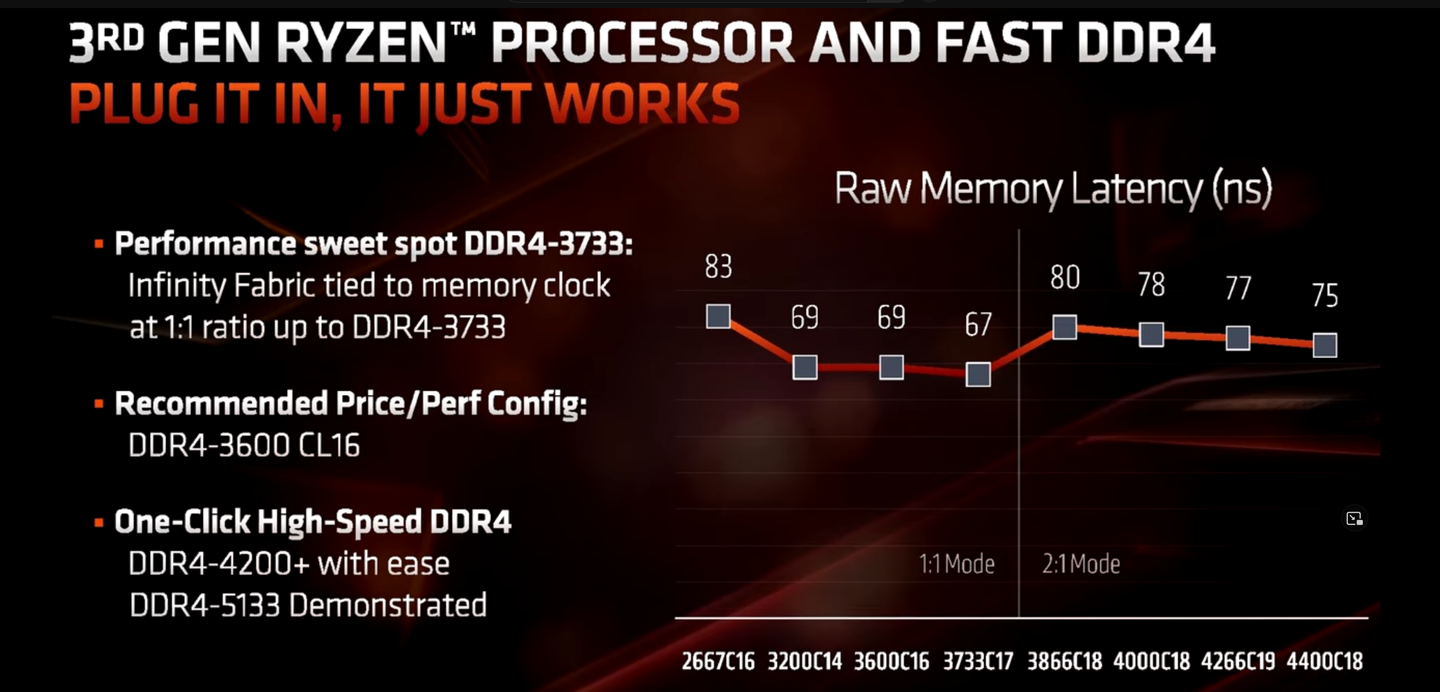

所以很多平台上就形成了一个比较常见的经验结论:DDR4 3600 左右,往往是一个比较平衡的位置。

它不是绝对真理,但为什么很多人都提这个数?因为在不少 Zen2 / Zen3 平台上,这个区间刚好兼顾了:

- 频率不低

- 分频压力不算大

- 稳定性也更容易拿到

对大多数装机用户来说,这种“甜点位”通常比硬冲极限更有价值。

APU 平台为什么常常更能冲

这个现象也挺有意思。

有些 APU 因为内部结构更集中,数据传输路径更短,所以在内存这件事上,往往没桌面版 Chiplet 平台那么容易被 FCLK 卡住。

说得直白一点就是:

路更短,信号更容易跑。

所以你会看到一些 APU 平台,在更高内存频率下依然能保持不错的配合状态,不分频上限也可能更高。

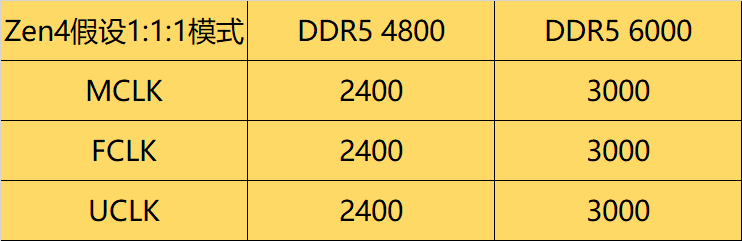

Zen4 + DDR5:为什么大家总提 6000

到了 Zen4,平台全面转向 DDR5,逻辑又和前面不太一样了。

因为 DDR5 起步就高,如果还按照老思路,要求所有关键频率都紧紧同步,那压力会非常大。

所以 Zen4 的重点不再是“强行追求以前那种齐步走”,而是换一种更现实的配合方式,让:

- DDR5 频率能上去

- UCLK 依然尽量别太掉队

- FCLK 保持在平台能接受的范围内

这也是为什么很多人会把 DDR5 6000 当成 Zen4 的常见推荐值。不是因为 6000 神奇,而是因为它经常处在一个比较均衡的区间里:

- 成本还算合理

- 稳定性普遍不错

- 性能也比较容易发挥出来

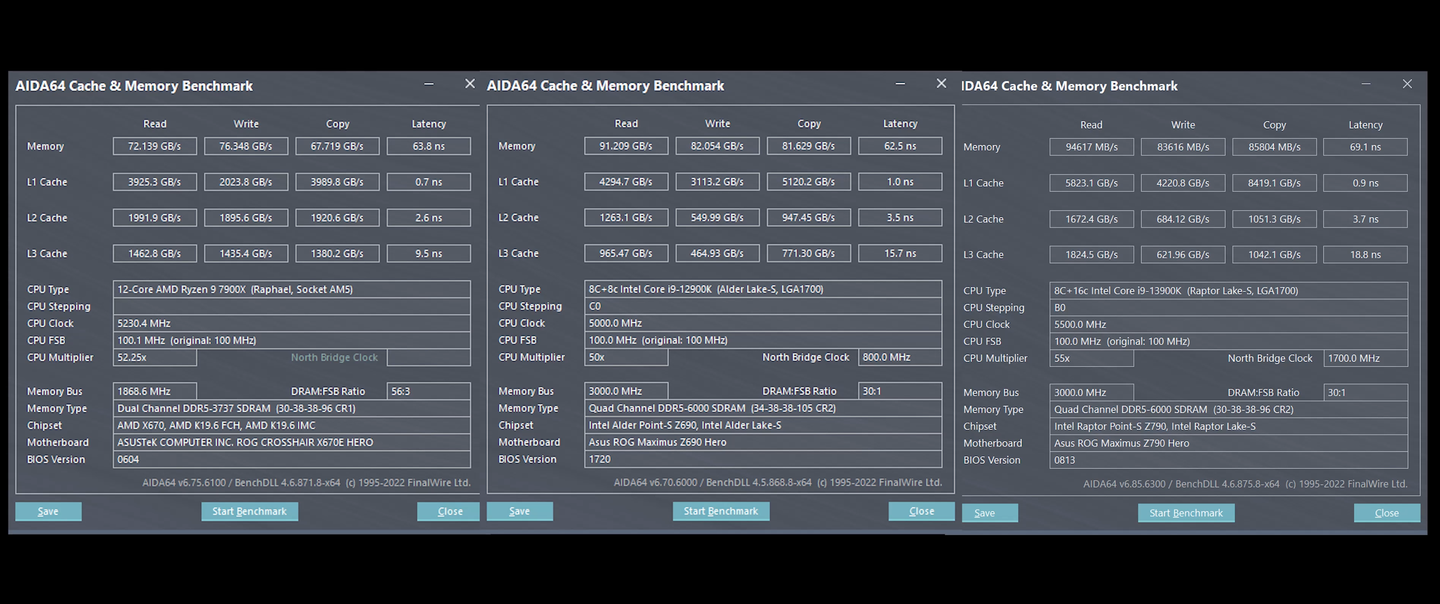

为什么 AMD 有时候频率不低,但带宽不如 Intel

这个问题很多人第一次看到都会疑惑。

明明同样是 DDR5 6000,为什么 AMD 有时带宽测试不如 Intel?

关键就在于平台内部结构不同。

Intel 和 AMD 走的不是同一条路。AMD 平台里,Infinity Fabric 这一段链路会更明显地影响整体表现。于是就可能出现一种情况:

- 内存本身已经很快

- 控制器也不算慢

- 但中间那条“运输通道”没有同步提升

最后整体表现,还是会被这一段拖住。

所以看锐龙内存,真的不能只盯着“内存频率”四个字。平台结构、频率比例、分频情况,都是一起决定结果的。

普通装机用户最该记住的 4 件事

1. 高频不一定等于高收益

尤其在锐龙平台上,如果为了追更高频率,结果换来了更激进的分频,那提升可能没有你想象中大。

2. 甜点位通常比极限位更重要

对日常装机、游戏、办公用户来说,稳定、好调、性价比合适,通常比“参数看起来最猛”更重要。

3. 不同代锐龙,玩法真的不一样

Zen1 / Zen+、Zen2 / Zen3、Zen4,这几代平台内存逻辑都不完全一样。老经验能参考,但不能生搬硬套。

4. 看锐龙内存,别只问一个“能上多少”

更有意义的问题其实是:

- 稳不稳定?

- 分频没有?

- UCLK 和 MCLK 是什么关系?

- FCLK 有没有拖后腿?

这些问题,比单纯看一个 MHz 数字更接近实际体验。

最后一句,给怕麻烦的人

如果你不想研究太多硬件术语,那你就记这一句:

锐龙内存的关键,不只是把频率拉高,而是让整条链路尽量配合顺。

所以很多时候,真正好的设置不是“最高频率”,而是“最平衡的频率”。

这也是为什么懂一点平台逻辑的人,在配锐龙内存时,更关注甜点位、分频和整体搭配,而不是只盯着参数表里那个最大的数字。